Up: Symbol Creation [Contents][Index]

4.1.8 Symbol example

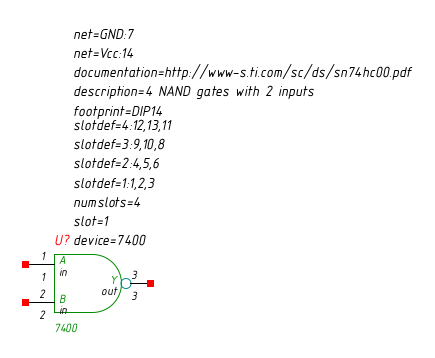

This section provides a simple example which tries to follow all of the above rules. This symbol is of a 7400 (NAND gate).

v 20031231 1

L 300 200 300 800 3 0 0 0 -1 -1

T 300 0 9 8 1 0 0 0 1

7400

L 300 800 700 800 3 0 0 0 -1 -1

T 500 900 5 10 0 0 0 0 1

device=7400

T 500 1100 5 10 0 0 0 0 1

slot=1

T 500 1300 5 10 0 0 0 0 1

numslots=4

T 500 1500 5 10 0 0 0 0 1

slotdef=1:1,2,3

T 500 1700 5 10 0 0 0 0 1

slotdef=2:4,5,6

T 500 1900 5 10 0 0 0 0 1

slotdef=3:9,10,8

T 500 2100 5 10 0 0 0 0 1

slotdef=4:12,13,11

L 300 200 700 200 3 0 0 0 -1 -1

A 700 500 300 270 180 3 0 0 0 -1 -1

V 1050 500 50 6 0 0 0 -1 -1 0 -1 -1 -1 -1 -1

P 1100 500 1300 500 1 0 1

{

T 1100 550 5 8 1 1 0 0 1

pinnumber=3

T 1100 450 5 8 0 1 0 2 1

pinseq=3

T 950 500 9 8 0 1 0 6 1

pinlabel=Y

T 950 500 5 8 0 1 0 8 1

pintype=out

}

P 300 300 0 300 1 0 1

{

T 200 350 5 8 1 1 0 6 1

pinnumber=2

T 200 250 5 8 0 1 0 8 1

pinseq=2

T 350 300 9 8 0 1 0 0 1

pinlabel=B

T 350 300 5 8 0 1 0 2 1

pintype=in

}

P 300 700 0 700 1 0 1

{

T 200 750 5 8 1 1 0 6 1

pinnumber=1

T 200 650 5 8 0 1 0 8 1

pinseq=1

T 350 700 9 8 0 1 0 0 1

pinlabel=A

T 350 700 5 8 0 1 0 2 1

pintype=in

}

T 300 900 8 10 1 1 0 0 1

refdes=U?

T 500 2250 5 10 0 0 0 0 1

footprint=DIP14

T 500 2450 5 10 0 0 0 0 1

description=4 NAND gates with 2 inputs

T 500 2850 5 10 0 0 0 0 1

net=Vcc:14

T 500 3050 5 10 0 0 0 0 1

net=GND:7

T 500 2650 5 10 0 0 0 0 1

documentation=http://www-s.ti.com/sc/ds/sn74hc00.pdf

This example produces the following (using lepton-schematic):

This is the same symbol with all the hidden text visible (via Edit → Show/Hide Inv Text):